使

H

# NY8TM52D

6 I/O 8-bit MTP-Based MCU with 4-key Touch Pad

手

$\mathbf{H}$

Version 1.0

Dec. 8, 2020

NYQUEST TECHNOLOGY CO. reserves the right to change this document without prior notice. Information provided by NYQUEST is believed to be accurate and reliable. However, NYQUEST makes no warranty for any errors which may appear in this document. Contact NYQUEST to obtain the latest version of device specifications before placing your orders. No responsibility is assumed by NYQUEST for any infringement of patent or other rights of third parties which may result from its use. In addition, NYQUEST products are not authorized for use as critical components in life support devices/systems or aviation devices/systems, where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user, without the express written approval of NYQUEST.

## **Revision History**

| Version | Date       | Description     | Modified Page |

|---------|------------|-----------------|---------------|

| 1.0     | 2020/12/08 | Formal release. | -             |

## **Table of Contents**

| 1. | 概刻  | <u>t</u> |                                                    | 7  |

|----|-----|----------|----------------------------------------------------|----|

|    | 1.1 | 功能       |                                                    | 7  |

| 1. | Ger | neral Do | escription                                         | 9  |

|    |     |          | es                                                 |    |

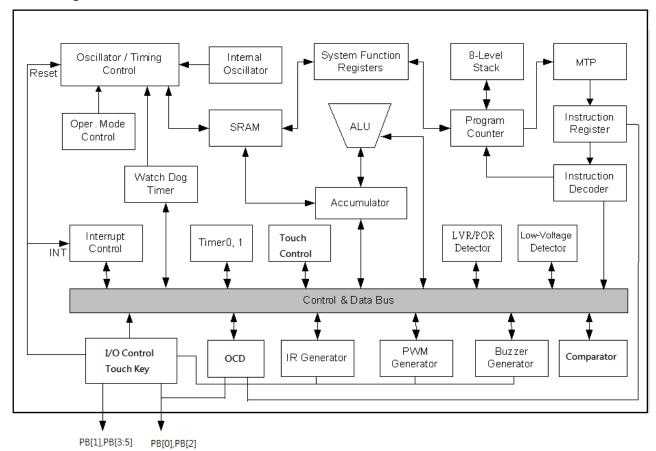

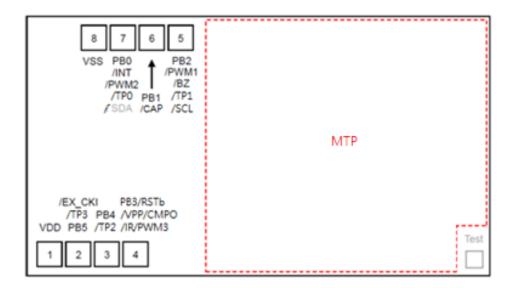

|    | 1.2 | Block D  | Diagram                                            | 11 |

|    |     |          | signment                                           |    |

|    |     |          | escription                                         |    |

|    | 1.4 | FIII Des | scription                                          | 13 |

| 2. | Mei | mory O   | Organization                                       | 14 |

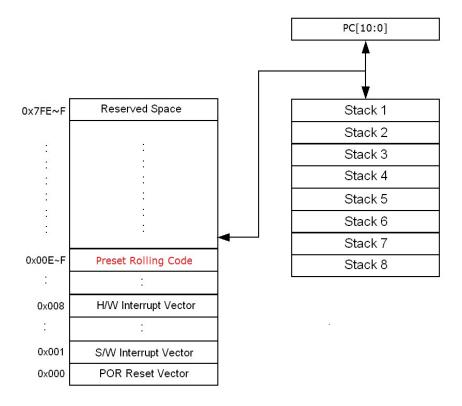

|    | 2.1 | Prograi  | m Memory                                           | 14 |

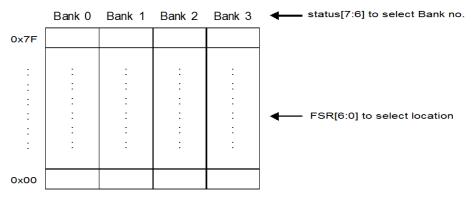

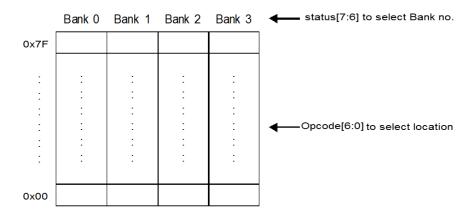

|    | 2.2 | SRAM/    | /Register Memory                                   | 15 |

| 3. | Fur | nction E | Description                                        | 18 |

|    | 3.1 |          | e Special Function Register                        |    |

|    |     | 3.1.1    | INDF (Indirect Addressing Register)                |    |

|    |     | 3.1.2    | TMR0 (Timer0 Register)                             |    |

|    |     | 3.1.3    | PCL (Low Byte of PC[10:0])                         |    |

|    |     | 3.1.4    | STATUS (Status Register)                           |    |

|    |     | 3.1.5    | FSR (Register File Selection Register)             | 19 |

|    |     | 3.1.6    | PortB (PortB Data Register)                        | 20 |

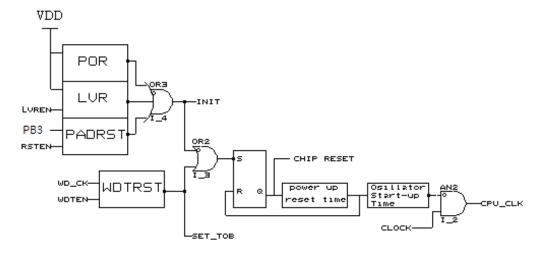

|    |     | 3.1.7    | PCON (Power Control Register)                      | 20 |

|    |     | 3.1.8    | BWUCON (PortB Wake-up Control Register)            | 20 |

|    |     | 3.1.9    | PCHBUF (High Byte of PC)                           | 21 |

|    |     | 3.1.10   | BPLCON (PortB Pull-Low Resistor Control Register)  | 21 |

|    |     | 3.1.11   | BPHCON (PortB Pull-High Resistor Control Register) | 21 |

|    |     | 3.1.12   | INTE (Interrupt Enable Register)                   | 21 |

|    |     | 3.1.13   | INTF (Interrupt Flag Register)                     | 22 |

|    |     | 3.1.14   | INTEDG (Interrupt Edge Register)                   | 23 |

|    |     | 3.1.15   | TMRH (Timer High Byte Register)                    | 23 |

|    |     | 3.1.16   | ANAEN (Analog Circuit Enable Register)             | 23 |

|    |     | 3.1.17   | PWM3RH (PWM3DUTY High Byte Register)               | 24 |

|    | 3.2 | T0MD I   | Register                                           | 24 |

| F-page  | Special Function Register                                                                                                                                                                                                                                                                              | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.3.1   | IOSTB (PortB I/O Control Register)                                                                                                                                                                                                                                                                     | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.3.2   | PS0CV (Prescaler0 Counter Value Register)                                                                                                                                                                                                                                                              | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.3.3   | BODCON (PortB Open-Drain Control Register)                                                                                                                                                                                                                                                             | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.3.4   | CMPCR (Comparator voltage select Control Register)                                                                                                                                                                                                                                                     | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.3.5   | PCON1 (Power Control Register1)                                                                                                                                                                                                                                                                        | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| S-page  | Special Function Register                                                                                                                                                                                                                                                                              | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

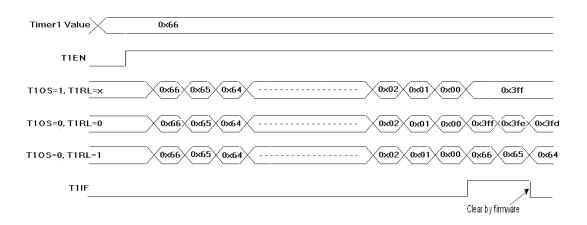

| 3.4.1   | TMR1 (Timer1 Register)                                                                                                                                                                                                                                                                                 | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.4.2   | T1CR1 (Timer1 Control Register1)                                                                                                                                                                                                                                                                       | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.4.3   | T1CR2 (Timer1 Control Register2)                                                                                                                                                                                                                                                                       | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

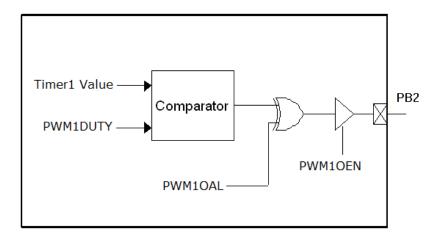

| 3.4.4   | PWM1DUTY (PWM1 Duty Register)                                                                                                                                                                                                                                                                          | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.4.5   | PS1CV (Prescaler1 Counter Value Register)                                                                                                                                                                                                                                                              | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

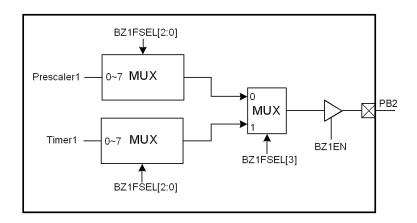

| 3.4.6   | BZ1CR (Buzzer1 Control Register)                                                                                                                                                                                                                                                                       | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.4.7   | IRCR (IR Control Register)                                                                                                                                                                                                                                                                             | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.4.8   | TBHP (Table Access High Byte Address Pointer Register)                                                                                                                                                                                                                                                 | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.4.9   | TBHD (Table Access High Byte Data Register)                                                                                                                                                                                                                                                            | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

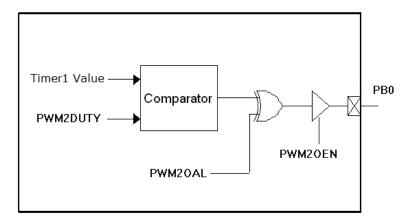

| 3.4.10  | P2CR1 (PWM2 Control Register1)                                                                                                                                                                                                                                                                         | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.4.11  | PWM2DUTY (PWM2 Duty Register)                                                                                                                                                                                                                                                                          | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

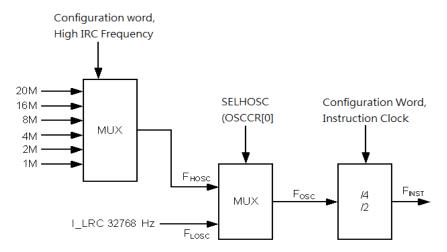

| 3.4.12  | OSCCR (Oscillation Control Register)                                                                                                                                                                                                                                                                   | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

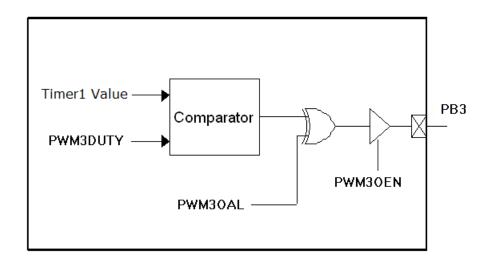

| 3.4.13  | P3CR1 (PWM3 Control Register1)                                                                                                                                                                                                                                                                         | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.4.14  | PWM3DUTY (PWM3 Duty Register)                                                                                                                                                                                                                                                                          | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| T-page  | Special Function Register                                                                                                                                                                                                                                                                              | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.5.1   | INTE3 (Interrupt Enable 3th Register)                                                                                                                                                                                                                                                                  | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.5.2   | INTF3 (Interrupt Flag 3th Register )                                                                                                                                                                                                                                                                   | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

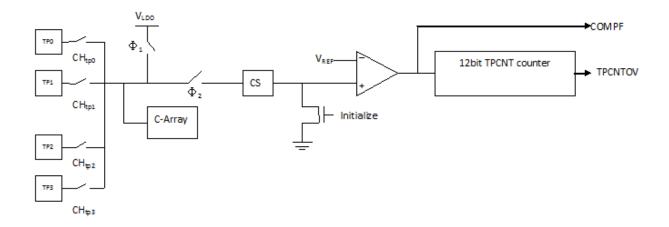

| 3.5.3   | TPCKS (Touch pad clock register)                                                                                                                                                                                                                                                                       | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.5.4   | CASR (Touch pad extra capacitance select register)                                                                                                                                                                                                                                                     | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.5.5   | TPCHS (Touch pad channel select register)                                                                                                                                                                                                                                                              | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.5.6   | TPCR (Touch pad control register)                                                                                                                                                                                                                                                                      | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.5.7   | TPCNTL (Touch pad low counter register)                                                                                                                                                                                                                                                                | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.5.8   | TPCNTH (Touch pad high counter register)                                                                                                                                                                                                                                                               | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.5.8   | TPPADEN (Touch pad enable register)                                                                                                                                                                                                                                                                    | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| I/O Por | rt                                                                                                                                                                                                                                                                                                     | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

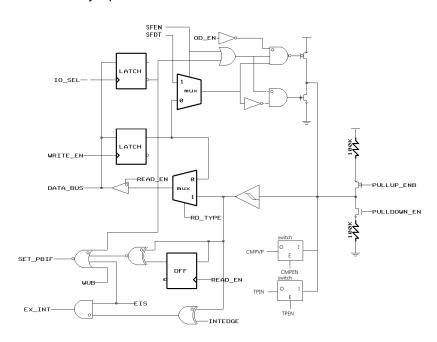

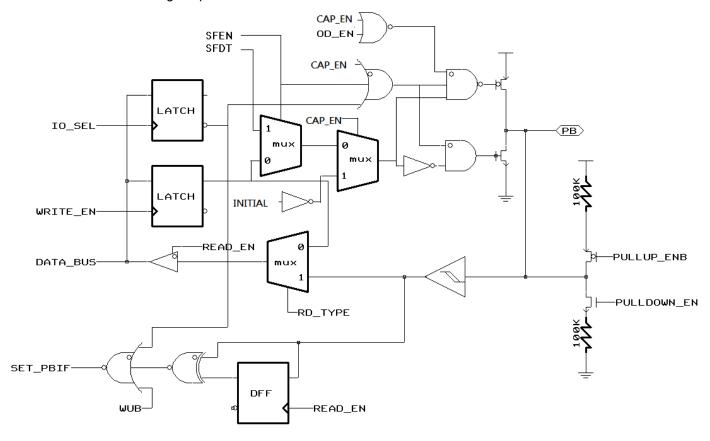

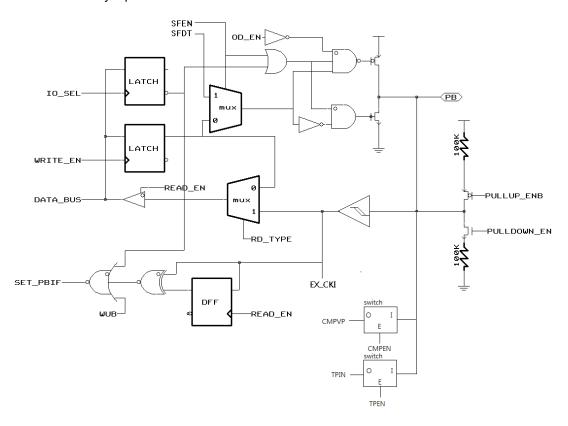

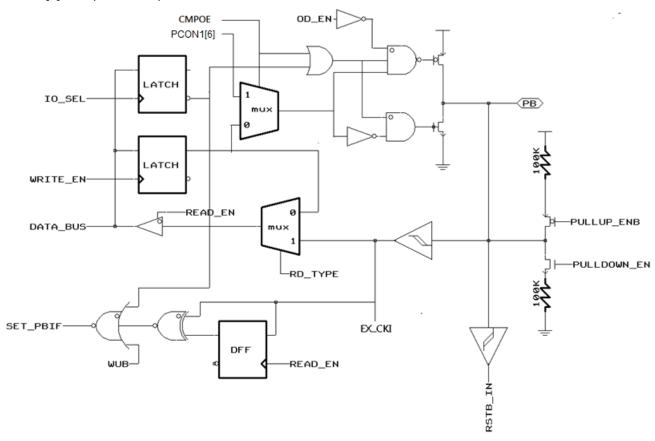

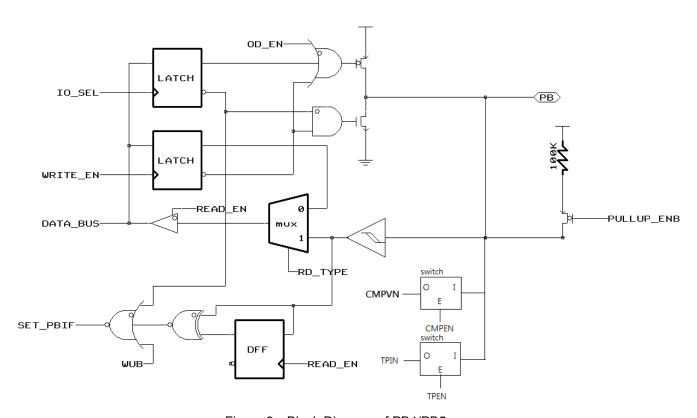

| 3.6.1   | Block Diagram of IO Pins                                                                                                                                                                                                                                                                               | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

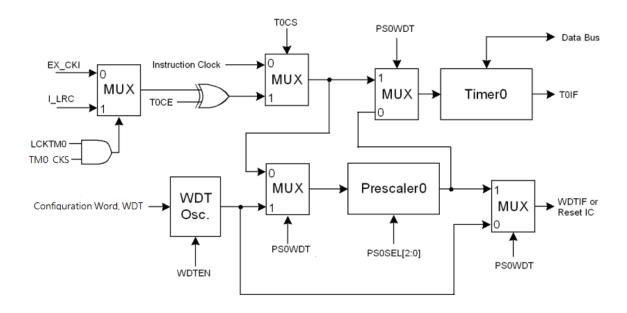

| Timer0  | )                                                                                                                                                                                                                                                                                                      | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

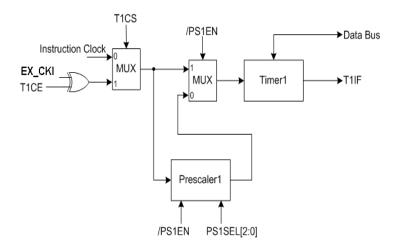

| Timer1  | /PWM1/Buzzer1                                                                                                                                                                                                                                                                                          | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | 3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>S-page<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10<br>3.4.11<br>3.4.12<br>3.4.13<br>3.4.14<br>T-page<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5<br>3.5.6<br>3.5.7<br>3.5.8<br>1/O Poi<br>3.6.1<br>TimerO | 3.3.2 PSOCV (Prescaler0 Counter Value Register) 3.3.3 BODCON (PortB Open-Drain Control Register) 3.3.4 CMPCR (Comparator voltage select Control Register) 3.3.5 PCON1 (Power Control Register1) S-page Special Function Register 3.4.1 TMR1 (Timer1 Register) 3.4.2 T1CR1 (Timer1 Control Register2) 3.4.3 T1CR2 (Timer1 Control Register2) 3.4.4 PWM1DUTY (PWM1 Duty Register) 3.4.5 PS1CV (Prescaler1 Counter Value Register) 3.4.6 BZ1CR (Buzzer1 Control Register) 3.4.7 IRCR (IR Control Register) 3.4.8 TBHP (Table Access High Byte Address Pointer Register) 3.4.9 TBHD (Table Access High Byte Data Register) 3.4.10 P2CR1 (PWM2 Control Register1) 3.4.11 PWM2DUTY (PWM2 Duty Register) 3.4.12 OSCCR (Oscillation Control Register) 3.4.13 P3CR1 (PWM3 Control Register1) 3.4.14 PWM3DUTY (PWM3 Duty Register) 3.5.1 INTE3 (Interrupt Enable 3th Register) 3.5.2 INTF3 (Interrupt Enable 3th Register) 3.5.3 TPCKS (Touch pad extra capacitance select register) 3.5.5 TPCHS (Touch pad control register) 3.5.6 TPCR (Touch pad low counter register) 3.5.7 TPCNTL (Touch pad low counter register) 3.5.8 TPPADEN (Touch pad enable register) |

| 3 10 |                                                                                                |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.10 | PWM3.                                                                                          |                                                                                                                                                                                                                                                                                             | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

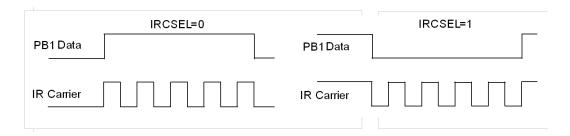

| 3.11 | IR Carri                                                                                       | ier                                                                                                                                                                                                                                                                                         | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

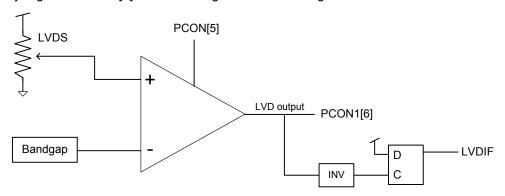

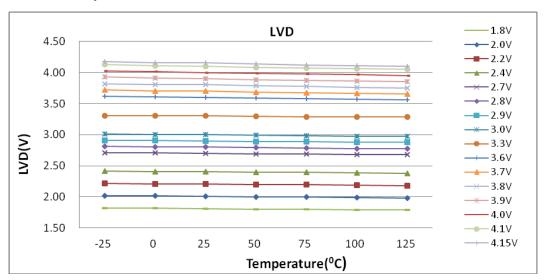

| 3.12 | Low Vo                                                                                         | Itage Detector (LVD)                                                                                                                                                                                                                                                                        | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

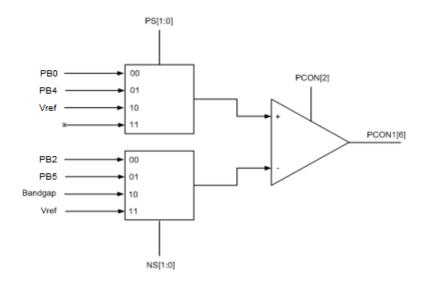

| 3.13 | Voltage                                                                                        | Comparator                                                                                                                                                                                                                                                                                  | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

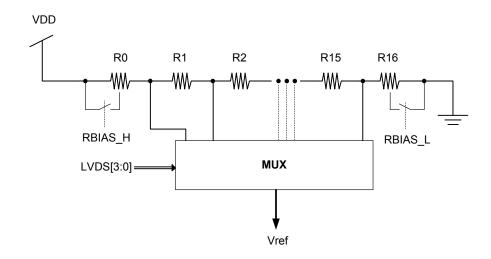

| 3.13 | .1 Con                                                                                         | nparator Reference Voltage (Vref)                                                                                                                                                                                                                                                           | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.14 |                                                                                                |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      |                                                                                                |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      |                                                                                                |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | •                                                                                              |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 3.16.2                                                                                         | ·                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 3.16.3                                                                                         | ·                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 3.16.4                                                                                         | PB Input Change Interrupt                                                                                                                                                                                                                                                                   | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 3.16.5                                                                                         | External Interrupt                                                                                                                                                                                                                                                                          | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 3.16.6                                                                                         | LVD Interrupt                                                                                                                                                                                                                                                                               | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 3.16.7                                                                                         | Touch pad comparator interrupt                                                                                                                                                                                                                                                              | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 3.16.8                                                                                         | Touch pad counter overflow interrupt                                                                                                                                                                                                                                                        | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.17 | Oscillat                                                                                       | ion Configuration                                                                                                                                                                                                                                                                           | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

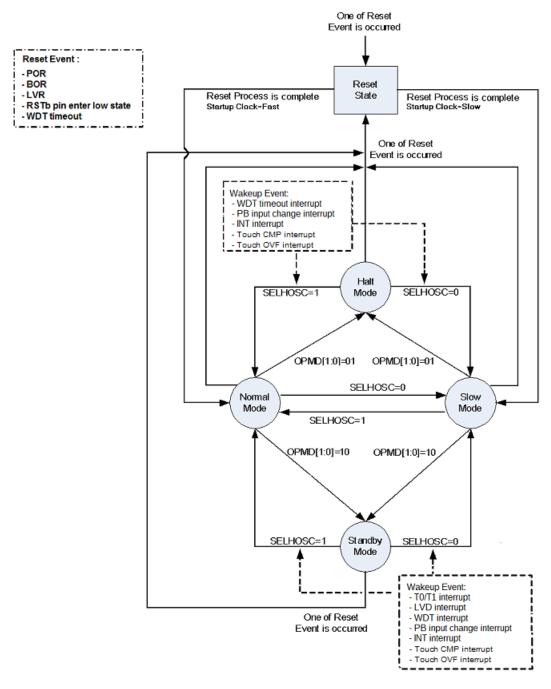

| 3.18 | Operati                                                                                        | ng Mode                                                                                                                                                                                                                                                                                     | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |